SONY

# **CXB1828ER**

## 2.5Gbps Laser Diode Driver

#### Description

The CXB1828ER is a high-speed monolithic laser diode driver. This IC can drive the data rate of 2.5Gbps and the modulation current of up to 50mA. The bias current of up to 50mA can be supplied and it is controlled by the built-in APC (automatic power control). The modulation current and bias current are designed to be linearly controlled by the voltage input to the control pin.

This IC has a built-in DFF, and through mode or DFF mode can be selected. In through mode the signal goes as it is, and in DFF mode the input signal is retimed by the external clock. The data input pin and the clock input pin can accept the differential input of PECL and CML, and the  $50\Omega$  termination resistors are provided in the IC.

The shutdown function which shuts down the modulation current and bias current, the activity error detect circuit which detects that the signal has no input, and the alarm output power-on reset circuit. Furthermore, the duty cycle control circuit which corrects the modulation output signal duty is included in this IC.

The CXB1828ER employs the 4.8mm  $\times 4.8$ mm of 32-pin plastic package, contributing to the miniaturization of the optical mode.

#### Features

- · Direct laser diode drive

- Maximum data rate of 2.5Gbps

- Power-on reset function

- Automatic power control (APC) for bias current

- Alarm function and shutdown function

- Differential PECL and CML inputs or AC coupled input

- · Internal duty cycle correction circuit

- Activity error detector function for laser safety

- Typical rise time is 80ps.

- Built-in 50Ω input termination resistor

- Compact package size: 4.8mm × 4.8mm

- Single +3.3V supply voltage

#### Applications

- Gigabit ethernet: 1.25Gbps

- SONET/SDH: 622Mbps, 2.5Gbps

#### Absolute Maximum Ratings

|                                    | U U               |              |    |

|------------------------------------|-------------------|--------------|----|

| <ul> <li>Supply voltage</li> </ul> | Vcc – Vee         | -0.3 to +6.0 | V  |

| • Data and clock inp               | out voltage diffe | erence       |    |

|                                    | Vd – Vdn          | 2.5          | V  |

| • Bias output curren               | t                 | 100          | mΑ |

| • Modulation output                | current           | 100          | mΑ |

| • Storage temperatu                | ire               |              |    |

|                                    | Tstg              | -65 to +150  | °C |

|                                    |                   |              |    |

#### **Recommended Operating Conditions**

| <ul> <li>Supply voltage</li> </ul> | Vcc – Vee     | 3.14 to 3.46 | V  |

|------------------------------------|---------------|--------------|----|

| • Operating ambien                 | t temperature |              |    |

|                                    | Та            | -40 to +85   | °C |

#### **Important Notes**

The IC requires SLOW turning power on and off. See Vcc rise and fall time in AC characteristics.

#### **Electrostatic Strength**

This IC has a very sensitive electrostatic strength, so care should be taken for handling.

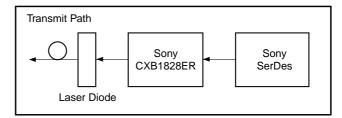

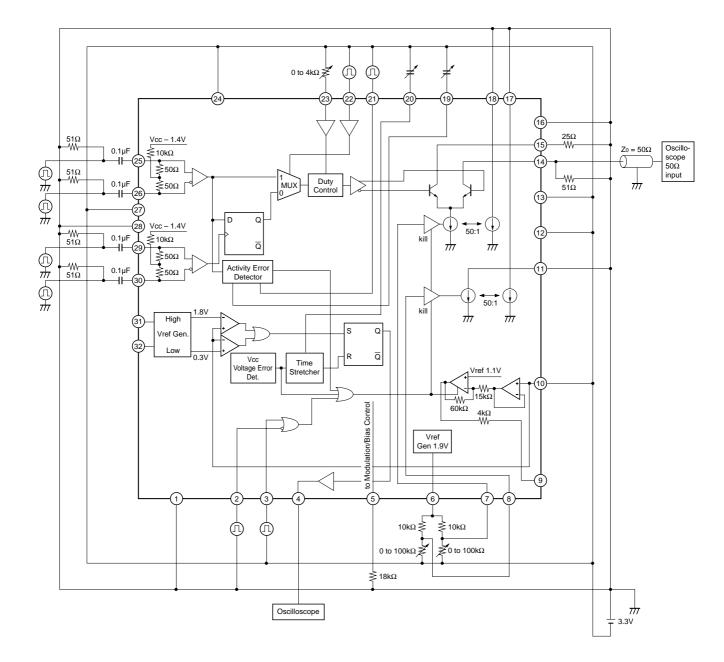

#### **Typical Transmit Block Diagram**

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

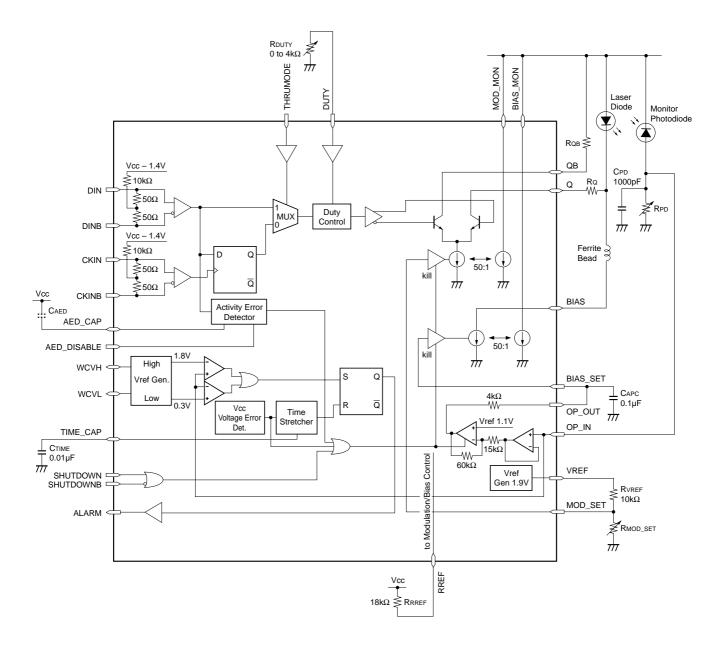

#### **Block Diagram** MOD\_MON BIAS\_MON DUTY Л Vcc - 1.4V QB ≩10kΩ Q DIN \$50Ω 1 MUX 0 Duty ≩50Ω Control DINB Vcc - 1.4V ≷10kΩ D Q CKIN I ≹50Ω 50:1 kill Q $\pi$ $\pi$ ≩50Ω CKINB 🛛 Activity Error BIAS Detecto AED\_CAP t 50:1 AED\_DISABLE kill 1.8V High $\pi$ $\pi$ WCVH Q s Vref Gen BIAS\_SET WCVL 4kΩ -₩-Low R Q OP\_OUT 0.3V Vcc Time tage Error Det. Vol Vref 1.1V Stretcher □ OP\_IN TIME\_CAP w 15kΩ \_\_\_\_\_\_ 60kΩ to Modulation/Bias Control Vref Gen 1.9V SHUTDOWN > VREF ⊐ MOD\_SET ALARM · RREF .

**Pin Assignment**

### **Pin Description**

| Pin<br>No. | Symbol    | Typical pin<br>voltage (V)<br>DC | I/O | Equivalent circuit        | Description                                                                                                                                         |

|------------|-----------|----------------------------------|-----|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | Vcc2      | 3.3                              |     |                           | Positive power supply.                                                                                                                              |

| 2          | SHUTDOWNB | 0 or Vcc                         | I   | $2 + \frac{10k\Omega}{3}$ | TTL input.<br>The modulation current and bias<br>current is shut down by inputting<br>the Low voltage to this pin. High<br>level when open.         |

| 3          | SHUTDOWN  | 0 or Vcc                         | I   | VEE2                      | TTL input.<br>The modulation current and bias<br>current is shut down by inputting<br>the High voltage to this pin. High<br>level when left open.   |

| 4          | ALARM     |                                  | 0   | Vcc2<br>(4)<br>VEE2       | TTL output.<br>High when the abnomality is<br>detected from the OP_IN pin<br>voltage. The abnormal voltage of<br>OP_IN is Vop < 0.3V or Vop > 1.8V. |

| 5          | RREF      |                                  |     | Vcc2                      | Connect an external resistor of 18kΩ between this pin and Vcc.                                                                                      |

| Pin<br>No. | Symbol   | Typical pin<br>voltage (V)<br>DC | I/O | Equivalent circuit     | Description                                                                                                                                                                                                               |

|------------|----------|----------------------------------|-----|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6          | VREF     | 1.9                              | 0   | Vcc2<br>26.4KΩ<br>VEE2 | Reference voltage output.<br>GND reference 1.9V.                                                                                                                                                                          |

| 7          | MOD_SET  | 0.2 to 2.0                       | I   |                        | Modulation current control.<br>The modulation current is<br>controlled by this pin voltage.                                                                                                                               |

| 8          | BIAS_SET | 0.2 to 2.0                       | I   | (8)<br>VEE2            | Bias current control.<br>The bias current is controlled by<br>the voltage of this pin.                                                                                                                                    |

| 9          | OP_OUT   |                                  | 0   | Vcc2                   | Internal operational amplifier<br>output.<br>Used for the bias current<br>automatic power control (APC).<br>The OP_OUT pin is connected to<br>the BIAS_SET pin. Connect a<br>0.1µF capacitor between this pin<br>and GND. |

| 10         | OP_IN    | 0.3 to 1.8                       | I   | Vcc2                   | The internal operational amplifier<br>input for the bias current automatic<br>power control (APC).                                                                                                                        |

| Pin<br>No. | Symbol   | Typical pin<br>voltage (V) | I/O | Equivalent circuit                        | Description                                                                                                                                                              |

|------------|----------|----------------------------|-----|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |          | DC                         |     |                                           |                                                                                                                                                                          |

| 11         | BIAS     |                            | 0   | Vcc1<br>(1)<br>Current<br>Source<br>VEEO2 | Laser bias current output.                                                                                                                                               |

| 12         | VeeO2    | 0                          |     |                                           | Negative power supply for the modulation and bias output.                                                                                                                |

| 13         | VEEO1    | 0                          |     |                                           | Negative power supply for the modulation output.                                                                                                                         |

| 14         | Q        |                            | 0   |                                           | Laser modulation current output.<br>Open collector output.                                                                                                               |

| 15         | QB       |                            | 0   | VEEO1 VEEO1                               | Complementary current output.<br>Connect the laser diode not to this<br>pin, but to the Q pin.                                                                           |

| 16         | VccO     | 3.3                        |     |                                           | Positive power supply for the modulation output.                                                                                                                         |

| 17         | BIAS_MON |                            | Ο   | Vcc1                                      | Bias current monitor.<br>1/50 of the bias current flows<br>to this pin. This pin is connected to<br>Vcc either through a resistor $1k\Omega$<br>or directly.             |

| 18         | MOD_MON  |                            | ο   | VEE1 (MOD_MON)<br>VEEO2 (BIAS_MON)        | Modulation current monitor.<br>1/50 of the modulation current<br>flows to this pin. This pin is<br>connected to Vcc either through a<br>resistor $1k\Omega$ or directly. |

| Pin<br>No. | Symbol      | Typical pin<br>voltage (V)<br>DC | I/O | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Description                                                                                                                                                                                                                                                                               |

|------------|-------------|----------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19         | AED_CAP     |                                  |     | Vcc2<br>30pF<br>19<br>500Ω<br>VEE2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Capacitor connection for the<br>activity error detector. If the active<br>detector function is not required,<br>this pin can be left open.<br>When a capacitor is connected<br>between the AED_CAP pin and<br>Vcc, the time till the error is<br>detected can be extended.                |

| 20         | TIME_CAP    |                                  |     | Vcc2<br>(20)<br>500Ω<br>30pF<br>VEE2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Capacitor connection for the alarm<br>power-on reset.<br>The period of the power-on reset<br>time is controlled by a capacitor<br>(recommended value is 0.01µF)<br>connected between the TIME_CAP<br>pin and GND.<br>If the ALARM function is not<br>required, this pin can be left open. |

| 21         | AED_DISABLE |                                  | I   | $Vcc2$ $(2)$ $(1)k\Omega$ | TTL input.<br>This pin controls the activity error<br>detector circuit.<br>When High (open or connected to<br>Vcc), the activity error detector<br>function is disabled. When Low<br>(connected to GND), the activity<br>error detector function is enabled.                              |

| 22         | THRUMODE    |                                  | I   | Vcc2<br>10kΩ<br>10kΩ<br>10kΩ<br>VEE2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TTL input.<br>When High (open or connected to<br>Vcc), the input data goes not<br>through the D flip-flop.<br>When Low (connected to GND),<br>the serial input data goes through<br>the D flip-flop within the chip.                                                                      |

| Pin<br>No. | Symbol | Typical pin<br>voltage (V)<br>DC | I/O | Equivalent circuit           | Description                                                                                                                                                                     |

|------------|--------|----------------------------------|-----|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23         | DUTY   |                                  |     | Vcc1                         | Resistor connection for the duty<br>cycle control.<br>When an external resistor is<br>connected between the DUTY pin<br>and GND, the modulation pulse<br>width can be expanded. |

| 24         | Vee2   | 0                                |     |                              | Negative power supply.                                                                                                                                                          |

| 25         | DIN    | PECL                             | I   | Vcc1<br>25<br>50Ω \$ 10kΩ    | Differential PECL and CML data inputs.<br>These two inputs are internally                                                                                                       |

| 26         | DINB   | CML                              |     | 26 50Ω ≶ 10kΩ<br>VEE1        | connected by 100 $\Omega$ and biased by 10k $\Omega$ to Vcc – 1.4V.                                                                                                             |

| 27         | Vee1   | 0                                |     |                              | Negative power supply.                                                                                                                                                          |

| 28         | Vcc1   | 3.3                              |     |                              | Positive power supply.                                                                                                                                                          |

| 29         | CKIN   | PECL                             | Ι   |                              | Differential PECL and CML clock<br>inputs.<br>These two inputs are internally                                                                                                   |

| 30         | CKINB  | CML                              | •   |                              | connected by $10k\Omega$ and biased by $10k\Omega$ to Vcc – $1.4V$ .                                                                                                            |

| 31         | WCVH   | 1.8                              |     | Vcc2<br>(31)<br>Vee2<br>Vee2 | Window comparator's higher<br>threshold voltage for ALARM.<br>The default high alarm assert<br>voltage for the comparator is 1.8V.                                              |

| Pin<br>No. | Symbol | Typical pin<br>voltage (V)<br>DC | I/O | Equivalent circuit                                 | Description                                                                                                                      |

|------------|--------|----------------------------------|-----|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 32         | WCVL   | 0.3                              |     | Vcc2<br>31<br>K<br>K<br>K<br>K<br>K<br>K<br>K<br>K | Window comparator's lower<br>threshold voltage for ALARM.<br>The default low alarm assert<br>voltage for the comparator is 0.3V. |

#### **Electrical Characteristics**

#### **DC Characteristics**

#### $(Vcc - Vee = 3.14 \text{ to } 3.46V, Ta = -40 \text{ to } +85^{\circ}C)$

| Item                                                        | Symbol   | Conditions                | Min.          | Тур.          | Max.          | Unit  |

|-------------------------------------------------------------|----------|---------------------------|---------------|---------------|---------------|-------|

| DC power supply voltage                                     | VDC      | Vcc – Vee                 | 3.14          | 3.3           | 3.46          | V     |

| Supply current<br>(DATA THRU MODE)                          | ICC_THRU | Iq = 0mA, IB = 0mA        |               | 62            | 84            | mA    |

| Supply current (D-FF MODE)                                  | ICC_DFF  | $I_Q = 0mA$ , $I_B = 0mA$ |               | 65            | 88            | mA    |

| Maximum modulation output current                           | Ідмах    |                           | 50            |               |               | mA    |

| Minimum modulation output current                           |          |                           |               |               | 7             | mA    |

| Modulation output voltage range                             | Vq       |                           | Vcc – 2       |               | Vcc           | V     |

| Maximum bias output current                                 | Івмах    |                           | 50            |               |               | mA    |

| Minimum bias output current                                 | Івмін    |                           |               |               | 3             | mA    |

| Bias output voltage range                                   | Vв       |                           | Vcc – 2       |               | Vcc           | V     |

| Modulation shutdown current                                 | IQSHD    |                           |               |               | 100           | μA    |

| Bias shutdown current                                       | Івѕно    |                           |               |               | 100           | μA    |

| DIN, CKIN input High voltage<br>(PECL)                      | Veih     | *1                        | Vcc –<br>1.17 |               | Vcc –<br>0.81 | V     |

| DIN, CKIN input Low voltage<br>(PECL)                       | Veil     | *1                        | Vcc –<br>1.84 |               | Vcc –<br>1.48 | V     |

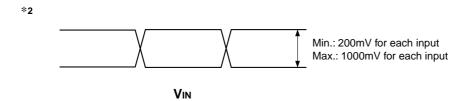

| DIN, CKIN differential input voltage (CML)                  | VIN      | *2                        | 400           |               | 2000          | mVp-p |

| Internal resistance between<br>DIN and DINB, CKIN and CKINB | Rdi, Rcк |                           | 70            |               | 130           | Ω     |

| Internal input reference voltage at DIN, DINB, CKIN, CKINB  | Veir     |                           |               | Vcc –<br>1.37 |               | V     |

| TTL input High voltage                                      | Vтін     |                           | 2.0           |               | Vcc +<br>0.3  | V     |

| TTL input Low voltage                                       | Vtil     |                           | -0.3          |               | 0.8           | V     |

| TTL input current High                                      | Ітін     |                           |               |               | 5             | μA    |

| TTL input current Low                                       | Ιτι∟     |                           | -250          |               |               | μA    |

| ALARM output High voltage                                   | Vтон     | lin = -0.4mA              | 2.4           |               | Vcc           | V     |

| ALARM output Low voltage                                    | VTOL     | lin = 2.0mA               | 0             |               | 0.5           | V     |

| VREF output voltage                                         | Vref     | lout = 0 to $500\mu$ A    | 1.80          |               | 2.05          | V     |

| WCVH output voltage                                         | Vwн      | Open voltage              | 1.70          |               | 2.05          | V     |

| WCVL output voltage                                         | Vwl      | Open voltage              | 0.28          |               | 0.37          | V     |

| Vcc voltage error detect voltage                            | Vcc_err  |                           | 2.59          |               | 3.08          | V     |

\*1 Since the internal input reference voltage may become lower than the Low level of ECL, input the signal into DIN and CKIN by AC coupling at the time of a single phase input.

#### **AC Characteristics**

(Vcc - VEE = 3.14 to 3.46V, Ta = -40 to +85°C)

| Item                                                    | Symbol | Conditions                                        | Min.  | Тур. | Max. | Unit |

|---------------------------------------------------------|--------|---------------------------------------------------|-------|------|------|------|

| Maximum data rate                                       | fdmax  |                                                   | 2.488 |      |      | Gbps |

| Maximum variable High pulse width by duty cycle control | tdelay | Data rate = 2.5Gbps                               | 100   |      |      | ps   |

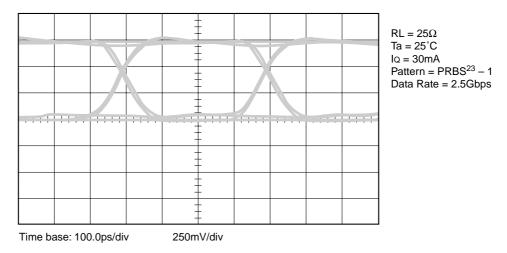

| Rise time (20 to 80%)                                   | tr     | $I_Q = 50 \text{mA}, \text{RL} = 25 \Omega$       |       | 80   |      | ps   |

| Fall time (80 to 20%)                                   | tf     | $I_Q = 50 \text{mA}, \text{RL} = 25 \Omega$       |       | 90   |      | ps   |

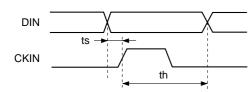

| DIN – CKIN setup time                                   | ts     | Rise and fall time of input = 130ps*3             | 30    |      |      | ps   |

| DIN – CKIN hold time                                    | th     | Rise and fall time of input = 130ps <sup>*3</sup> | 50    |      |      | ps   |

| Vcc rise time                                           | tvccr  | 10 to 90%                                         | 5     |      |      | ms   |

| Vcc fall time                                           | tvccf  | 90 to 10%                                         | 5     |      |      | ms   |

\*3

Setup time, Hold time

#### **DC/AC Characteristics for the APC Circuit**

$(Vcc - V_{EE} = 3.14 \text{ to } 3.46\text{V}, Ta = -40 \text{ to } +85^{\circ}\text{C})$

| Item                                                | Symbol    | Conditions | Min. | Тур.    | Max. | Unit |

|-----------------------------------------------------|-----------|------------|------|---------|------|------|

| OP_IN input voltage range                           | VI_OP     |            |      | Fig. 15 |      | V    |

| OP_OUT output maximum voltage                       | Vo_opmax  |            |      |         | 2.0  | V    |

| OP_OUT output minimum voltage                       | Vo_opmin  |            | 0.2  |         |      | V    |

| Minimum OP_OUT output voltage at shutdown condition | Vo_opsdn  |            |      |         | 0.2  | V    |

| OP_IN input current                                 | II_OP     |            | -2.0 |         | 1    | μA   |

| OP_OUT output source current                        | Io_opsorc |            |      |         | 4    | μA   |

| OP_OUT output sink current                          | Io_opsink |            |      |         | 4    | μA   |

| APC operational amplifier gain                      | Av        |            |      | 12      |      | dB   |

| Monitor photodiode current range                    | Impd      |            | 10   |         | 1000 | μA   |

#### **Functional Block Description**

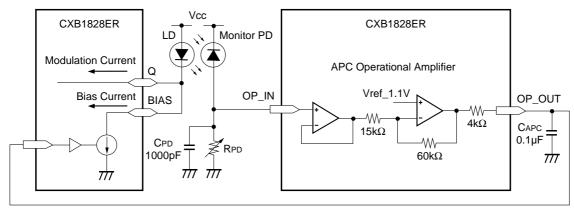

#### APC (Automatic power control)

The APC loop consists of the laser driver and APC operational amplifier. The APC operational amplifier is configured as an inverting integrator. It is the input voltage that is derived from the monitor current by the monitor photodiode and an external resistor RPD to OP\_IN.

The input voltage is inverted and the output from OP\_OUT. The bias current is controlled by inputting the output to the BIAS\_SET pin. The bias current is set by RPD. A capacitor CPD with a value of 1000pF works for stability and reduces the noise. Use CAPC (recommended value  $0.1\mu$ F) between the OP\_OUT pin and VEE. CAPC controls the rapid rise of the OP\_OUT pin when the shutdown is cancelled, and suppresses the excess current flowing to the laser diode.

Fig.1. APC Function Block Diagram

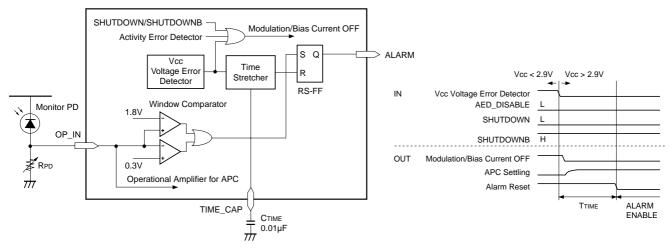

#### Alarm function

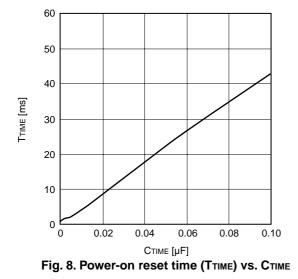

This circuit is for the APC operation. When the input OP\_IN is provided with an excess voltage or minimal voltage, the window comparator output goes High, and this signal is latched resulting in the output of alarm signal. The WCVH and WCVL pin voltages are the upper and the lower threshold values of the window comparator for ALARM. The default value of WCVH is 1.8V and that of WCVL is 0.3V. If the voltage of OP\_IN is lower than WCVL or higher than WCVH, ALARM signal is asserted High. This alarm signal returns to Low only by the Vcc power-on reset function. Power-on reset time (TTIME) is set by the external capacitor put between the TIME\_CAP pin and VEE. (Refer to Fig. 8.) It is necessary for the alarm signal output to be Low forcibly because the excess voltage or minimal voltage may be applied to the OP\_IN pin till the APC operation completes. The recommended value of the capacitor is 0.01µF.

#### Fig.3. Timing Chart of Alarm Function

#### Data input

The PECL/CML signal is input to the data buffer at a maximum data rate of 2.5Gbps. This input pin is biased by the reference bias voltage (Vcc – 1.4V) for the AC coupling input. An on-chip 100 $\Omega$  resistor is put between the DIN and DINB pins. The data buffer has the frequency detector and input amplitude voltage detector for the Activity Error Detector (AED).

#### Clock input

The PECL/CML clock is input to the clock buffer at a maximum data rate of 2.5GHz. This input pin is biased by the reference bias voltage (Vcc – 1.4V) for the AC coupling input. An on-chip 100 $\Omega$  resistor is put between the CKIN and CKINB pins.

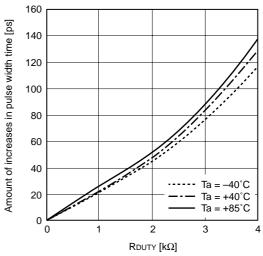

#### Signal duty cycle correction

The output pulse width can be extended as shown in Fig.9 by connecting an external resistor between the DUTY pin and VEE, and setting its resistor value from  $0\Omega$  to  $4k\Omega$ . The output pulse width can be extended up to 100ps (min.). Short the DUTY pin to VEE when not want to vary the duty.

Fig.4. Duty Cycle Control

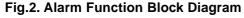

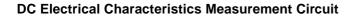

#### Bias current and modulation current control

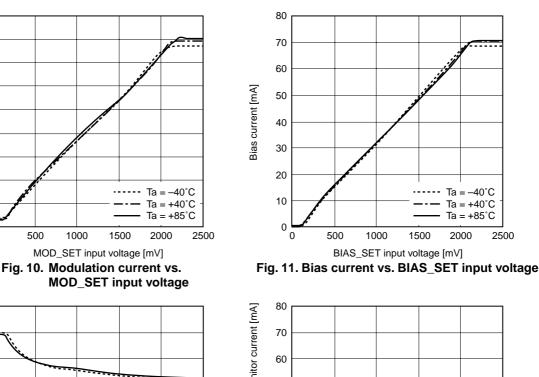

The bias current and modulation current can be controlled linearly by the voltage input to the BIAS\_SET and MOD\_SET pins as shown in Figs.10 and 11. The voltage applied to the BIAS\_SET and MOD\_SET pins can be set by the external resistor between the VREF pin and VEE. Refer to Fig.5.

Fig.5. Modulation/Bias Control

#### Bias current and modulation current monitor

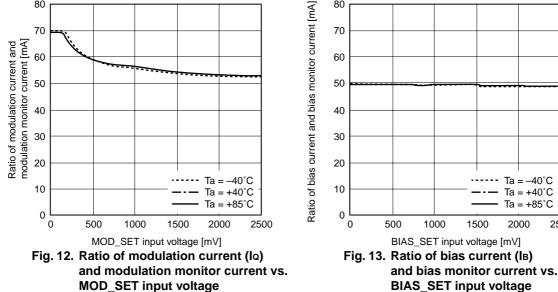

This circuit monitors the bias and modulation current. The BIAS\_MON and the MOD\_MON pins should be connected to Vcc either directly or through a resistor. The modulation current and monitor current are in the rate of approximately 50:1. (Refer to Fig.12 and Fig.13.)

#### Thru-mode

When this pin is High or connected to Vcc, the input data goes not through the internal flip-flop. If this pin is grounded the input data goes through the D flip-flop.

#### **Shutdown function**

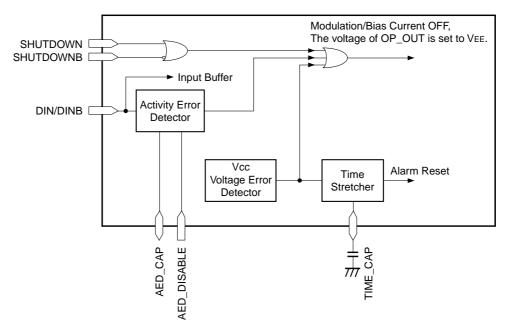

This circuit disables the output current, that is, the bias and modulation current is turned off and used to shut off the laser. And the voltage of OP\_OUT is set to VEE. The function block diagram for all of the shutdown mechanism for the circuit is shown in Fig.6. The shutdown functions when one of the following conditions is met.

- 1) SHUTDOWN is High.

- 2) SHUTDOWNB is Low.

- 3) The activity error detector detects an error of the DIN/DINB input signal.

- 4) The voltage error detector detects Vcc is below 2.59 to 3.08V.\*

- (\* The bias current may flow at approximately Vcc = 2.0V.)

Fig.6. Shutdown Function Block Diagram

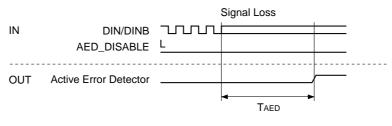

#### Activity error detect function

The activity error detect circuit monitors the DIN/DINB input signal, and shuts down the output current when this circuit determines that the input data signal has no input. The conditions where the input signal is determined to be no signal are when the input data signal logic is not varied over a period of the time set by the user and when the voltage swing is too small (< 100mVpp-diff). Either of these conditions is met, the shutdown circuit is enabled and the modulation current and laser bias current are shut down.

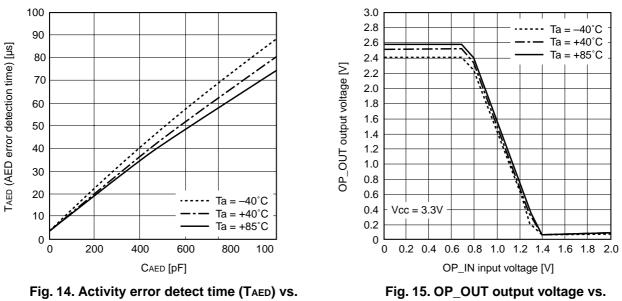

If needed, the time till the activity error detect can be extended. Fig.14 shows the graphs of the activity error detection time (TAED) vs. CAED. When the activity error detect function is not required, connect the AED\_DISABE pin to Vcc or leave it the pin open.

Fig.7. Timing Chart of AED Function

#### **AC Electrical Characteristics Measurement Circuit**

#### **Application Circuit**

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

Modulation current [mA]

Fig. 9. Increment of output pulse width vs. RDUTY

CAED

**OP\_IN** input voltage

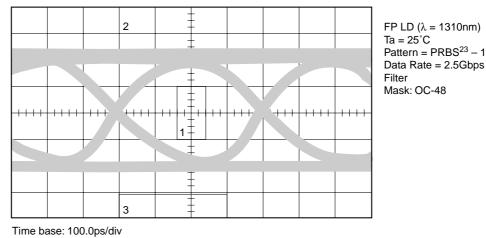

Fig. 16. Electrical Output Waveform

Fig. 17. Optical Output Waveform

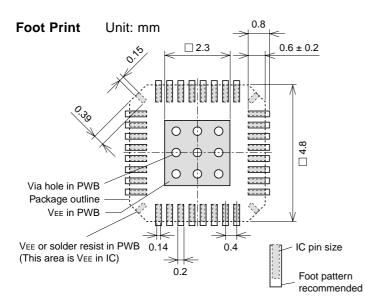

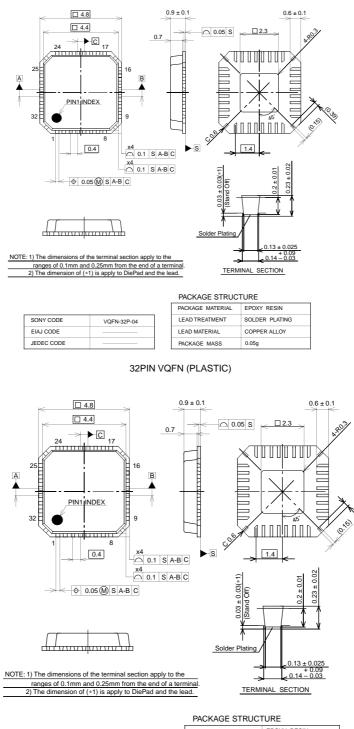

#### Package Outline

Unit: mm

32PIN VQFN (PLASTIC)

| SONY CODE  | VQFN-32P-04 |

|------------|-------------|

| EIAJ CODE  |             |

| JEDEC CODE |             |

| LEAD PLATING SPECIFICATIONS |

|-----------------------------|

|-----------------------------|

| ITEM               | SPEC.           |

|--------------------|-----------------|

| LEAD MATERIAL      | COPPER ALLOY    |

| SOLDER COMPOSITION | Sn-Bi Bi:1-4wt% |

| PLATING THICKNESS  | 5-18µm          |

| PACKAGE MATERIAL | EPOXY RESIN    |

|------------------|----------------|

| LEAD TREATMENT   | SOLDER PLATING |

| LEAD MATERIAL    | COPPER ALLOY   |

| PACKAGE MASS     | 0.05g          |

|                  |                |